edt test compression|Test Compression : vendor Abstract: Scan chains are the fundamental building blocks for DFT, and testing for scan integrity is the first step in a robust test methodology. This article describes scan integrity . Em “Avatar: O Caminho Da Água”, James Cameron regressa ao mundo de Pandora numa nova aventura repleta de ação e emoção. Ambientada mais de uma década após os .

{plog:ftitle_list}

webSlow Horses — Season 1. What to Know. Critics Consensus. Slow Horses refreshes the espionage genre by letting its band of snoops be bumbling, with Gary Oldman giving a masterclass in frumpy.

One of the most common hardware test compression technique is EDT. Tessent TestKompress is the tool that can generate the decompressor and compactor logic at the RTL level. As shown in Figure 2, the decompressor drives the scan chain inputs and the compactor connects from the .JTAG is the acronym for Joint Test Action Group, a name for the group of people .

The Introduction to EDT (TestKompress) High Test Quality & Low Test Cost. 27 June Park sung-chul. Contents. Today’s DFT Challenge Comparison Factors of TestKompress Comparing . Test compression is a technique implemented for test compression. It creates & embeds the test compression logic into the design. It further extends ATPG to generate compressed test patterns. Abstract: Scan chains are the fundamental building blocks for DFT, and testing for scan integrity is the first step in a robust test methodology. This article describes scan integrity .

With scan ATPG compression, which is based on EDT technology, circuitry receives compressed data from the tester, decompresses it within the chip, and then compacts the response for. Popular scan techniques include Illinois Scan, a technique that involves connecting many internal scan chains to a common scan channel, and embedded deterministic test (EDT), which employs a combination of . Test compression sounds like magic. Read on to learn how this trick is done. Large, complex ICs are viable because their design meets test as well as functional requirements. The article describes a strategy for addressing this tension by the appropriate augmentation of scan compression technologies with techniques that minimize the number of test interfaces required and enable reduced pin .

Embedded Deterministic Test | EDT | EDT Architecture in Details | Signals Used in EDT | Pins used in EDT | DFT Compression Logic | DFT Syllabubs | DFT Topi. A new and comprehensive method to boost performance of sequential test compression and ATPG operations and prevents ATPG from assigning specified values to many inputs in order to cut down a time-consuming backtracking process needed to resolve conflicts leading to compression aborts. On-chip test compression has quickly established itself as .

Text compression algorithms play a vital role in reducing the size of data while maintaining its integrity. One approach to achieving text compression is through the divide and conquer methodology. In this tutorial, we will explore text compression algorithms using the divide and conquer technique. Introduction to Divide and Conquer AlgorithmsOn-chip test compression has quickly established itself as one of the mainstream design-for-test (DFT) methodologies. It assumes that a tester delivers test patterns in a compressed form, and on-chip decompressors expand them into actual data loaded into scan chains. This paper presents a new and comprehensive method to boost performance of sequential test . Embedded deterministic test (EDT) has continued to deliver more compression, which has been quite effective at containing test costs. For many designs, standard test compressions is enough, but ICs for use in automotive and medical devices require a higher manufacturing test quality, which translates to more test patterns and longer test times.

This paper presents a novel test-data volume-compression methodology called the embedded deterministic test (EDT), which reduces manufacturing test cost by providing one to two orders of magnitude reduction in scan test data volume and scan test time. The presented scheme is widely applicable and easy to deploy because it is based on the standard .Test compression is a technique used to reduce the time and cost of testing integrated circuits.The first ICs were tested with test vectors created by hand. It proved very difficult to get good coverage of potential faults, so Design for testability (DFT) based on scan and automatic test pattern generation (ATPG) were developed to explicitly test each gate and path in a design.

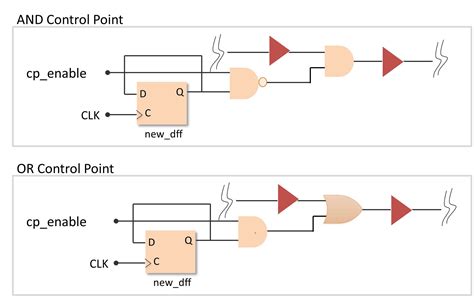

Reduced Test Time The patented embedded deterministic test (EDT) technology incorporated into Tessent TestKompress reduces both test time and data volume without any loss in test coverage. Consistent compression levels, regardless of design architecture are achieved by effective X masking without the need for X bounding, test points, orThis paper proposes an innovative test compression technology for system-on-chip (SoC) designs to share scan input channels across multiple cores which use EDT [1] compression. A new DFT compression architecture is proposed to separate control and data channels such that the control channels can be individually accessible, whereas data channels can be shared . The TestKompress� product is based on a test pattern compression scheme the company calls embedded deterministic test (EDT) and was described in detail in the paper �Embedded .

Using EDT Test Points to reduce test time and cost

EDT Test PointsEmbedded deterministic test has been created specifically to deal with embedded compression to reduce pattern volume for compressed patterns. . Embedded test compression was commercially introduced over a decade ago and has scaled to well beyond the 100X range envisioned when it was first introduced. However, growing gate .LLMLingua-2: Data Distillation for Efficient and Faithful Task-Agnostic Prompt Compression. microsoft/LLMLingua • • 19 Mar 2024. Additionally, our model is 3x-6x faster than existing prompt compression methods, while accelerating the end-to-end latency by 1. 6x-2. 9x with compression ratios of 2x-5x.

emerson apparatus compression tester

Test compression hardware blocks such as EDT are utilized in large industrial designs to compress scan test data in order to decrease scan test time and volume. During pattern generation for EDT-based designs, some faults cannot be detected due to linear dependency and insufficient encoding capacity of EDT. These faults called EDT Aborted (EAB) faults cause a . 相对来说,大部分的scan IO 都是复用function IO 的,很少专门为scan 留IO. 在评估增加多少个scan IO 时,可以使用 analyze_compression命令分析。 在Tdf ATPG 模式下的 EDT coverage 损失. 1. 在 ATPG capture cycles时, EDT logic (LFSR) 会将X 驱动到scan chain. 2.

VLSI Test Principles and Architectures Ch. 6 - Test Compression – P. 46 Space compaction X-masking X’s can be masked off right before the response compactor . Test Compression – P. 59 EDT (TestKompression ) architecture. EE141 60 VLSI Test Principles and Architectures Ch. 6 - Test Compression – P. 60 TestKompress stimuli compression. Embedded Deterministic Test | EDT | Advantages | Disadvantages | Data Volume Reduction in EDT | Test Application Time reduction in EDT | EDT Compression | .Test cost has become a critical issue for large industrial integrated circuits. Various test compression techniques have been adopted in the industry to reduce test cost. However, appropriate input and output channel counts must be selected to utilize the test compression technology best. This paper presents an efficient and effective method to estimate the test . This paper presents novel methods of reducing test time and enhancing test compression for system-on-chip (SoC) designs armed with embedded deterministic test (EDT)-based compression logic. The ability of the proposed scheme to improve the encoding efficiency and test compression, while reducing test application time, is accomplished by appropriate .

The paper illustrates the benefits of the proposed technology in both the enhancement of compression ratios and the flexibility of test compression planning in a core-based SoC design flow. This paper proposes an innovative test compression technology for system-on-chip (SoC) designs to share scan input channels across multiple cores which use . A new low-power test compression scheme, called Dcompress, is proposed for launch-on-capture transition fault testing by using a new seed encoding scheme, a new design for testability architecture, and a new low-power test application procedure.The new seed encoding scheme generates seeds for all tests by selecting a primitive polynomial that encodes all tests . Embedded Deterministic Test | EDT | EDT Architecture in Details | Signals Used in EDT | Pins used in EDT | DFT Compression Logic | DFT Syllabubs | DFT Topi. About Press Copyright Contact us Creators Advertise Developers Terms Privacy Policy & Safety How YouTube works Test new features NFL Sunday Ticket Press Copyright .

Test costs for large industrial designs increase rapidly in recent years. On-chip test compression hardware has become a pragmatic technology to cut down the overall test costs by reducing the test data volume. Determining the input and output channel counts of test compression hardware that results in minimum test data volume is thus a critical issue. In this article, . The past decade observed compression of test data as an effective method for reducing the volume of test data and test application time. In order to work with the increasing clock frequencies in a contemporary design, a low fill rate of care bits is exploited due to the result of combinational logic [].Hence, the fill rate of the every determined test pattern did not exceed .

Even advanced test infrastructures such as X-compactor and X-masking are vulnerable to such an attack. In this work, we perform a detailed security analysis of one of the DfT techniques known as the Embedded Deterministic Test (EDT), which is used in the test compression tool Tessent TestKompress.

compression - Free download as PDF File (.pdf), Text File (.txt) or view presentation slides online. This document provides an overview of Embedded Deterministic Testing (EDT) implemented by Tessent TestKompress. EDT uses deterministic ATPG to achieve high test compression and reduce test time while maintaining high test quality. TestKompress inserts . Text compression, commonly referred to as Gzip or Brotli compression, is a technique used to minimize the size of text files transmitted from a web server to a user’s browser. By reducing the file size, text compression will improve the performance of WordPress sites, as well as any other web application, making it a crucial aspect of web .

The Introduction to EDT (TestKompress)

.jpg)

Test Pattern Compression Saves Time and Bits

WEBAt 5ft 7in and 121lb, Kelsi Monroe looks like a doll who would gladly let you take her clothes off. She was born on June 30th, 1994. Kelsi has natural auburn hair and brown eyes. Her bra size is a b, and her measurements are 32B-24-36. She was born and raised in Fort Lauderdale, Florida.

edt test compression|Test Compression